Alternative Computing Technologies (ACT) Lab

School of Computer Science

Georgia Institute of Technology

Tabla is an accelerator generator framework for geometric machine learning algorithms. It is an open source project under the Apache license.

About Design Builder

TABLA's Design Builder generates the accelerator for the given learning algorithm.

Design Builder and predesigned templates

Design Builder contains a generic template for stochastic gradient descent, which is used across all range of statistical machine learning algorithms. These accelerator templates are pre-designed by expert hardware designers and resued for learning algorithms that use stochastic gradient descent. Moreover, the template provides the intefacing logic between accelerators and the rest of the system.

Source: D. Mahajan, J. Park, E. Amaro, H. Sharma, A. Yazdanbaksh, J. Kim, H. Esmaeilzadeh. TABLA: A Unified Template-based Framework for Accelerating Statistical Machine Learning. In HPCA, 2016

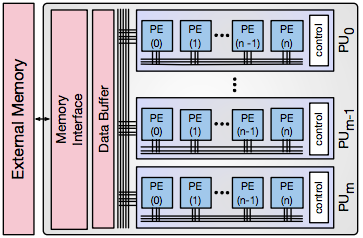

As shown in the figure, all the learning algorithms above have one thing in common: stochastic gradient descent. Given the programmer's implementation of the gradient function, the design builder generates the corresponding synthesizable Verilog code.

The figure above is a clustered template architecture that is scalable, general, and highly customizable. The design builder shrinks or expands this template design considering the degree of parallelism in the Data Flow Graph and the availability of the resources in the target FPGA. The design builder first extracts the maximum number of parallel operations from the Data Flow Graph and select the total number of the Processing Engines accordingly.

License

This source code is published under the terms specified in the Apache license.

Copyright 2016 Hadi Esmaeilzadeh

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Patrons